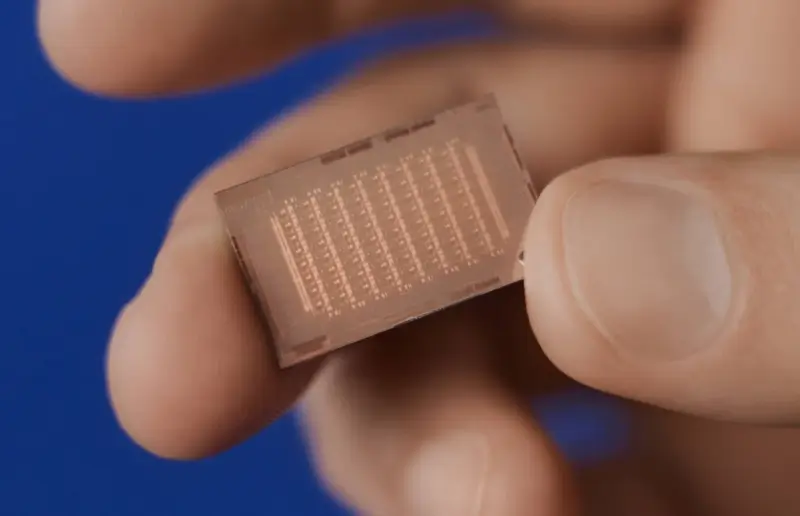

Der KI-Chip von Meta wurde mit dem 5-nm-Prozess von TSMC hergestellt

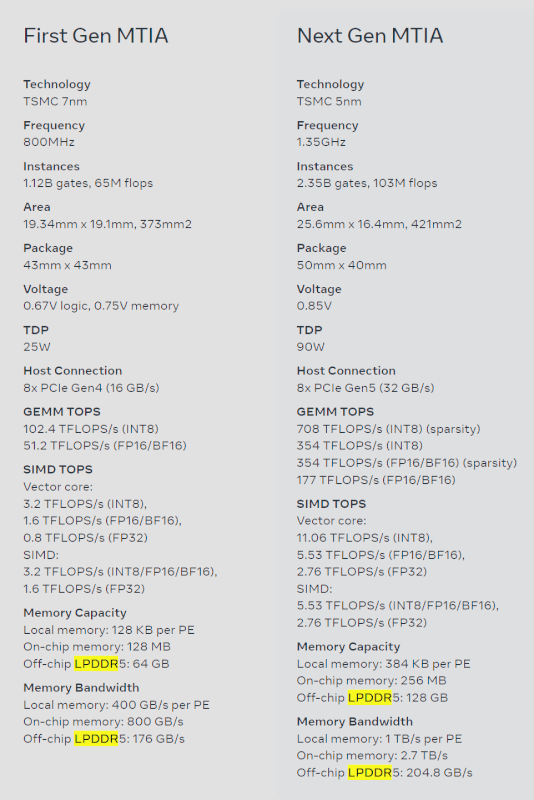

Meta hat uns gerade einen ersten Blick auf ihren KI-Chip der nächsten Generation – MTIA – geworfen, der ein Upgrade gegenüber ihrem aktuellen Chip, MTIA v1, darstellt. Der neue MTIA-Chip wird auf dem neueren 5-nm-Prozessknoten von TSMC hergestellt, wo der ursprüngliche MTIA-Chip auf 7 nm hergestellt wurde.

Der neue MTIA-Chip (Meta Training and Inference Accelerator) ist „im Wesentlichen darauf ausgerichtet, das richtige Gleichgewicht zwischen Rechenleistung, Speicherbandbreite und Speicherkapazität zu liefern“, das für die individuellen Anforderungen von Meta verwendet wird. Wir haben gesehen, dass die besten KI-GPUs der Welt HBM-Speicher verwenden, wobei HBM3 auf den KI-Chips der Serien Hopper H100 und AMD Instinct MI300 von NVIDIA verwendet wird, aber der Meta verwendet DRAM-Speicher mit geringem Stromverbrauch (LPDDR5) anstelle von Server-DRAM oder LPDDR5-Speicher.

Der Social-Networking-Riese hat seinen MTIA-Chip als KI-Inferenzbeschleuniger der ersten Generation entwickelt, der intern für die KI-Arbeitslast von Meta entwickelt wurde. Das Unternehmen sagt, dass seine Deep-Learning-Empfehlungsmodelle „eine Reihe von Erfahrungen mit unseren Produkten verbessern“ .

Das langfristige Ziel von Meta und ihre Reise mit dem KI-Inferenzprozessor besteht darin, die effizienteste Architektur für die einzigartigen Arbeitslasten von Meta bereitzustellen. Das Unternehmen fügt hinzu, dass KI-Workloads für die Produkte und Dienstleistungen von Meta immer wichtiger werden und die Effizienz ihrer MTIA-Chips ihre Fähigkeit verbessern wird, ihren Benutzern auf der ganzen Welt die besten Erlebnisse zu bieten.

Meta erklärt auf ihrer Website für MTIA: „Die Architektur dieses Chips ist im Wesentlichen darauf ausgerichtet, das richtige Gleichgewicht zwischen Rechenleistung, Speicherbandbreite und Speicherkapazität für die Bereitstellung von Ranking- und Empfehlungsmodellen bereitzustellen. Als Schlussfolgerung sollten wir sogar in der Lage sein, eine relativ hohe Auslastung zu liefern.“ wenn unsere Batch-Größen relativ gering sind. Indem wir uns auf die Bereitstellung einer übergroßen SRAM-Kapazität im Vergleich zu typischen GPUs konzentrieren, können wir in Fällen, in denen die Batch-Größen begrenzt sind, eine hohe Auslastung bieten und ausreichende Berechnungen bereitstellen, wenn wir größere Mengen potenziell gleichzeitiger Arbeit haben.

Dieser Beschleuniger besteht aus einem 8x8-Gitter aus Verarbeitungselementen (PE). Diese PEs bieten eine deutlich verbesserte Leistung bei dichter Datenverarbeitung (3,5-fach gegenüber MTIA v1) und bei geringer Datenverarbeitung (7-fache Verbesserung). Dies ist zum Teil auf Verbesserungen in der Architektur zurückzuführen, die mit dem Pipelining spärlicher Berechnungen verbunden sind. Es liegt auch daran, wie wir das PE-Netz versorgen: Wir haben die Größe des lokalen PE-Speichers verdreifacht, die Größe des On-Chip-SRAM verdoppelt, die Bandbreite um das 3,5-fache erhöht und die Kapazität von LPDDR5 verdoppelt.

Aktuelle prozessor - cpu

-

31 Oktprozessor - cpu

-

16 Sepprozessor - cpu

AMD Ryzen AI 7 PRO 360 entdeckt

-

04 Sepprozessor - cpu

Intel gewinnt großen KI-Chipkunden

-

04 Sepprozessor - cpu

Exklusiv von Intel hergestellte Ladenschubladen

-

29 Augprozessor - cpu

Großer Leistungsschub für Ryzen-CPUs

-

28 Augprozessor - cpu

Intel-Aktien könnten im Kampf mit TSMC und NVIDIA

-

28 Augprozessor - cpu

AMD soll gehackt worden sein

-

27 Augprozessor - cpu

Intel präsentiert Lunar Lake-, Xeon 6- und Guadi 3