Die neue COUPE-Technologie von TSMC ist im Jahr 2026 fertig

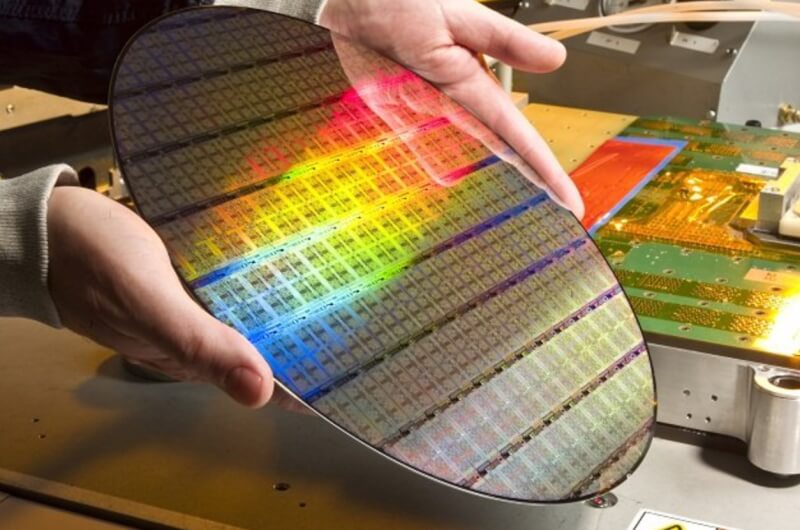

Die Taiwan Semiconductor Manufacturing Company (TSMC) hat auf dem Technologiesymposium von TSMC in Nordamerika im Jahr 2024 ihre neuesten Halbleiterprozesse, fortschrittlichen Verpackungen und 3D-IC-Technologien für KI-Innovationen der nächsten Generation vorgestellt. Bei der Veranstaltung stellte TSMC seine neue A16-Technologie vor, an der die Industrie teilnimmt -führende Nanoblatt-Transistoren mit einer innovativen rückseitigen Stromversorgungslösung für die Produktion im Jahr 2026, mit „deutlich verbesserter Logikdichte und Leistung“.

TSMC stellte außerdem seine neue System-on-Wafer-Technologie (TSMC-SoW) vor, eine innovative Lösung, die „revolutionäre Leistung auf Wafer-Ebene“ für zukünftige KI-Anforderungen für Hyperscale-Rechenzentren bietet. Die COUPE-Technologie der nächsten Generation nutzt die SoIC-X-Chip-Stacking-Technologie, um einen elektrischen Chip auf einen photonischen Chip zu stapeln, was laut TSMC die niedrigste Impedanz an der Chip-zu-Chip-Schnittstelle und eine höhere Energieeffizienz als herkömmliche Methoden bietet.

TSMC plant, COUPE im Jahr 2025 für Pluggables mit kleinem Formfaktor zu qualifizieren, woraufhin im Jahr 2026 die Integration in die CoWoS-Verpackung als Co-Packaged Optics (CPO) folgen wird, wodurch optische Verbindungen direkt in das Chipgehäuse integriert werden. TSMC hat auch angedeutet, dass es an einer neuen Technologie arbeitet, die Chips über die Rückseite des Chips selbst mit Strom versorgt, was KI-Chips und andere Prozessoren im Jahr 2026 und darüber hinaus beschleunigen wird. TSMC erklärte in seiner Pressemitteilung: „TSMC entwickelt die Compact Universal Photonic Engine (COUPE™)-Technologie, um das explosive Wachstum der Datenübertragung zu unterstützen, das mit der Nachfrage nach KI-Technologie einhergeht.

COUPE nutzt die SoIC-X-Chip-Stacking-Technologie, um einen elektrischen Chip auf einen photonischen Chip zu stapeln. Dies bietet die niedrigste Impedanz an der Chip-zu-Chip-Schnittstelle und eine höhere Energieeffizienz als herkömmliche Methoden. TSMC plant, COUPE im Jahr 2025 für Pluggables mit kleinem Formfaktor zu qualifizieren, gefolgt von der Integration in die CoWoS-Verpackung als Co-Packaged Optics (CPO) im Jahr 2026, wodurch optische Verbindungen direkt in das Gehäuse integriert werden.

Aktuelle prozessor - cpu

-

31 Oktprozessor - cpu

-

16 Sepprozessor - cpu

AMD Ryzen AI 7 PRO 360 entdeckt

-

04 Sepprozessor - cpu

Intel gewinnt großen KI-Chipkunden

-

04 Sepprozessor - cpu

Exklusiv von Intel hergestellte Ladenschubladen

-

29 Augprozessor - cpu

Großer Leistungsschub für Ryzen-CPUs

-

28 Augprozessor - cpu

Intel-Aktien könnten im Kampf mit TSMC und NVIDIA

-

28 Augprozessor - cpu

AMD soll gehackt worden sein

-

27 Augprozessor - cpu

Intel präsentiert Lunar Lake-, Xeon 6- und Guadi 3